KWIK circuit is common the problem solves 15Msps 18 the driver design of ADC considers a factor

[introduction] ADC driver is the crucial compose that data collects signal catenary to design builds module. ADC driver is used at executing a lot of crucial functions, if input signal extent to adjust, Chan Duan is changed to poor cent, eliminate in all modular deflection, often use at realizing filter wave. This technical know-how and integrated knowledge (common problem solves KWIK) circuit (the signal of the output that need branch that FAQ) note discusses how to input signal generation classics to adjust from Chan Duan, undertake to signal n changes the function requirement that with ensuring its satisfy ADC full span.

Common problem solves: For 15Msps 18 what factor should consider when ADC design inputs driver

Brief introduction

ADC driver is the crucial compose that data collects signal catenary to design builds module. ADC driver is used at executing a lot of crucial functions, if input signal extent to adjust, Chan Duan is changed to poor cent, eliminate in all modular deflection, often use at realizing filter wave. This technical know-how and integrated knowledge (common problem solves KWIK) circuit (the signal of the output that need branch that FAQ) note discusses how to input signal generation classics to adjust from Chan Duan, undertake to signal n changes the function requirement that with ensuring its satisfy ADC full span.

Answer this common question for the help, we will use LTC6228 (a low noise, low course of lack fidelity, high speed outputs operation amplifier to course) with LTC2387-18 SAR ADC. We will use noise meter to consider indication design right signal catenary the influence of the integral SNR function of the solution.

Graph 1. – realizes Chan Duan to divide changeover to difference with n changeover through adjusting

Design norms give typical examples

To this exemple, if design requirement norms expresses 1 to show, input signal comes for 0V 5V sine wave. This design will use the ADC driver circuit that the graph shows 1 times first and last. The function of this circuit is will odd end input signal changeover, adjust, shift outputs signal for proper poor cent, the below one level with the ground and signal so that it can be relaxed medium catenary (namely ADC) join.

To analyse a scheme 1 shows the performance of circuit, we compare use letter a confusion of voices (SNR) , the noise that gets each degree is contributed and use its at integral computation. The spectrum noise density of the SNR of the LTC2387-18 ADC that uses in computation and LTC6228 all comes from the norms in relevant data manual.

Ask an attention, to this exemple, the influence of negligible 1/f noise, because of area of 1/f of target frequency outclass, and yuan of parts of an apparatus of make choice of (if the graph is shown 1 times) it is OK that the course is optimized utmost ground reduces noise contribution.

Design skill / note

1. undertakes choosing between only power source and double power source when, should consider following a few factors: Because the abundant of signal catenary estimates a demand, only power source may mean signal amplitude to reduce, this may bring about SNR to reduce; Power supply of double power source must produce course of negaive electricity cause, increased complexity, but as a result of usable abundant the quantity increases, signal amplitude is OK taller, because of circumstance of only power source of prep above of this SNR function. From the watch 1 can see, we were used + the asymmetry power source of 7V/-3V, configuration of voltage of this kind of power source can offer sufficient abundant capacity to output limits in order to ensure the input is mixed to be able to maintain.

2.VBias is shown 1 times like the graph, this signal uses at changing the output signal n of the first class to need to match place with ADC input in all modular voltage n. From the graph 1 can see, this comes true simply through using resistor voltage divider to come, among them fiducial voltage Vref uses as source.

Capacitance C5 is used at eliminating the noise that voltage divider produces.

Attention:

? The impedance of driver network should be equal to the impedance of feedback network. This are in cannot use interior to slant buy electric current is quits when the function very important. This kind of configuration will ensure by slant the additional and maladjusted voltage that buy electric current introduces can be reduced.

? If use interior to slant,buy offsets function, should use tall resistance, in order to reduce the power comsumption of network of this voltage divider.

3. is reduce lack fidelity error, RC filter should use high quality electric capacity (like C0G (NP0) ) with resistor.

4. uses the standard resistance that is more than computational value.

If 5. does not care power comsumption problem, criterion the feedback resistor of two class and gain resistance can fall to 301 Ω , in order to improve the SNR performance of ADC and driver signal catenary.

Design stage

(discussion reference pursues 1)

? Signature is rectified and n is changed

? Use changeover function begs solution R1

![]()

What should notice is, to low resistance, the voltage noise of LTC6228 takes dominant place. Increase as resistor, resistor noise begins to take dominant place. Continue to increase as resistor, voltaic noise takes dominant place.

If choose the resistance of R2 to be 499 Ω , the noise that designs and power comsumption can acquire good balance.

Beg solution R1

? Computational VBias voltage is worth. This is use Vi and Vo in all modular voltage will finish. The target is the output of amplifier of the first class n changeover is 2.048V.

Vocm = 2.048V and Vicm = 2.5V

Calculate next Vbias, following place show:

? Computational rate , ensure the bias voltage that achieves place to need (Vbias) . Ω of hypothesis R8 = 499 can bring a foot to be in implementation to balance impedance in the input, calculate next R7. The noise of voltage divider network is divided by C5 filter

? Circuit noise analyses:

? The first class is outputted – voltage noise computation

The total voltage noise that output of the first class carries () can use calculation leaving type:

Among them:

The voltage noise of – operation amplifier,

The noise that impedance of source of * of noise of – electric current causes

– resistor noise

Computation the noise gain of the first class:

The voltage noise that noise of the electric current that seek solution causes is contributed. According to LTC6228 data manual,

? The 2nd class is outputted – voltage noise computation

Use same measure to calculate the total voltage noise of the 2nd class![]() .

.

Use formula 1 and above calculative value, of the 2nd class for![]() :

:

![]()

? Noise bandwidth computation

Computation the effective noise bandwidth of each class, with be voltage noise changeover virtual value noise.

Use 2 rank one of filter Step is significant noise bandwidth

Use the following formula to seek solution BWn of effective noise bandwidth. Here, k is the corrective factor of LPF of referenced brick wall, in this exemple it is 1.22, n is the rank number of filter.

The 2nd Step is significant noise bandwidth: 3 rank Filter

? The changeover of noise spectrum density to virtual value noise

various frequency spectrum density changeover is noise of equivalent virtual value.

![]()

Seek solution

Seek solution

? Total noise of computational ADC driver

The total difference of computational ADC driver divides voltage noise.

? ADC noise meter calculates

Beg the ADC voltage noise that solves full span to input signal. Use 4.096Vp or 2.9Vrms, SNRadc = 95.7dB.

? Signal catenary SNR is calculated

The ADC drive that gives according to computation and ADC noise meter calculate anticipated SNR performance.

A. Full span inputs signal

B. – 1.7dBFS inputs signal:

Among them – 1.7dBFS = 2.38VRMS

The design is emulated

Graph 1 in the function of circuit is to use LTSpice to emulate a tool to undertake emulation, whether to accord with main goal norms in order to decide.

If the result that gets from emulation testing stand pursues 2- graph is shown 6 times

Graph 2. – inputs signature to rectify

Graph 3. Output in all modular voltage VOCM

Graph 4: Difference divides output

Graph 5 RMS differs minute of noise

Graph 6. Total noise, ADC + driver

Measure an outcome

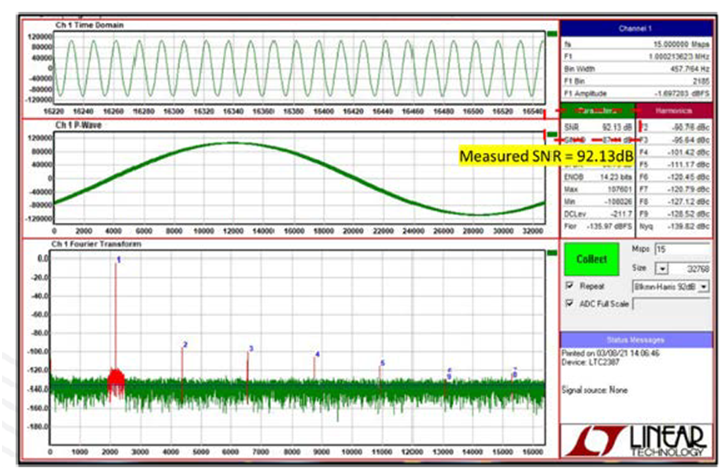

Use LTC6228 is evaluated demonstrate board evaluate with LTC2387-18 demonstrate board get measure an outcome. To this exemple, input signal setting is – 1.7dBFS. The actual measurement SNR of this signal catenary is 92.13 DB. This SNR (93.1 DB) that goes out than computation as a result is low about 1 DB. The difference of 1 DB is probable because the parasitism effect of circuit board and the blame that use the tolerance of yuan of parts of an apparatus to bring about are ideal,be effect. To realize expectant full span SNR, increase measured value 1.7dB, the result will achieve 93.83dB, the target SNR function that prep above circuit designs.

Design parts of an apparatus

The total SNR that – of graph 7 measures, ADC + driver

Reference material

LTSPICE? It is a high-powered SPICE III graph of emulation software, principle collects tool and weaveform to examine implement, compositive enhance function and model, simplified the emulation of switch manostat, linear manostat and signal catenary circuit.

ADI company offers extensive technical guideline to be used at building academic base. It is below a few already was proved useful and be worth to read the technical guideline with understanding more information.

Noise of amplifier of operation of MT-047 –

Noise of amplifier of operation of MT-048 – concerns: 1/f noise, RMS noise and equivalent noise bandwidth

The operation amplifier of system of only the limit of MT-049 – always outputs noise meter to calculate

MT-050 – 2 rank operation amplifier of the system always outputs noise meter to calculate

Avoid duty statement: The article is reprint an article, reprint this article purpose to depend on passing more information, the person that copyright puts in original work ‘s charge is all. If involve work copyright issue,article place uses video, picture, written language, contact please small make up undertake handling.