Why to carry put meeting generation to hand in more lack fidelity?

[introduction]The engineer expresses to had been encountered, when the output that collects carry to put with oscillograph is undee, voltage place is inputted in some, originally very perfect sine wave appeared to lost true case, but knowing is the account that carry puts or other transient cause. After the motion that in understanding the engineer uses puts a kind, the author concludes: Carry gives off those who showed an input to make more lack fidelity appearance.

The engineer expresses to had been encountered, when the output that collects carry to put with oscillograph is undee, voltage place is inputted in some, originally very perfect sine wave appeared to lost true case, but knowing is the account that carry puts or other transient cause. After the motion that in understanding the engineer uses puts a kind, the author concludes: Carry gives off those who showed an input to make more lack fidelity appearance.

Major engineer may be right this phenomenon is very new, had not heard this name even. The article will system and introduce what carry puts thoroughly to hand in more lack fidelity: The basic technology framework that the account that it produces, carry puts exceeds lack fidelity impact to handing in, and in the light of hand in more lack fidelity how do we undertake ameliorative.

Carry puts the classification that is based on craft

Carry puts it is basic and OK to be based on craft respect cent is: Bipolar, JFET, CMOS3 is planted framework type, also have be based on the BiFET that 3 kinds of types derive above and CMOS Zero-drift framework, every kinds of framework has each advantage each, this paragraphic and main it is to be aimed at 3 kinds of basic frameworks to undertake elaborating.

Bipoalr inputs a framework

Interior of graph 1 ADA4806-1 inputs a framework

Interior of graph 1 ADA4806-1 inputs a framework

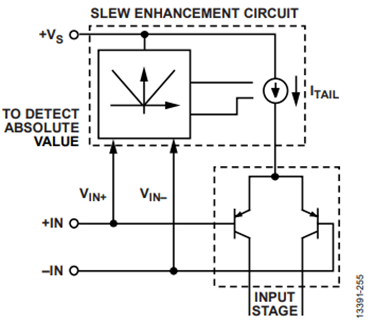

Pursue on (graph 1) the input framework that is ADA4806-1, signal comes over to enter ambipolar knot PNP to be in charge of directly, this is typical Bipolar framework; Dynatron is voltaic control electric current parts of an apparatus, drive capability is stronger, rate is rapid, compression is tall, noise is less.

Because the input has canal of a pair of PNP only extremely, so the input of ADA4806-1 can achieve next orbit only, fall in the circumstance of ± 5V power supply for instance, input in all modular voltage – 5.1V arrives + 4V.

JFET inputs a framework

Interior of graph 2 ADA4622-1 inputs a framework

Interior of graph 2 ADA4622-1 inputs a framework

Pursue on (graph 2) the input framework that is ADA4622-1 interior, pipe of a pair of JFET is entered directly after signal is inputted. FET is voltage control electric current parts of an apparatus, input impedance is particularly tall, it is voltage drive parts of an apparatus, do not need basically to input electric current, input loop is simpler.

Because the input has canal of a pair of JFET only extremely, so the input of ADA4622-1 can achieve next orbit only, fall in the circumstance of ± 5V power supply for instance, input in all modular voltage – 5.2V arrives + 4V.

CMOS inputs a framework

Interior of graph 3 ADA4530-1 inputs a framework

Pursue on (graph 3) it is framework of ADA4530-1 interior input, pipe of a pair of MOSFET is entered directly after signal is inputted. Regard voltage as control parts of an apparatus likewise, MOSFET photograph compares JFET and character, input impedance is taller, the use that makes accordingly is put in maladjusted electric current and slant the parameter of respect of buy electric current is better. MOSFET is counteractive to electrostatic discharge ability not beautiful, this kind of parts of an apparatus is in carry discharge road, front needs to add normally on diode (as above graph pursues place of 3 yellow casing is shown) undertake protective, the raceway groove of MOSFET is in the surface, unlike JFET is inside body, the carry of reason JFET input is put in noise respect function more exceedingly good.

Pursue on (graph 3) ADA4530-1 input class is in charge of to MOSFET only, so the input can achieve next orbit only, below the circumstance of odd 4.5V power supply, input voltage limits 0-3V.

In 3 kinds of when above introduction carry puts basic frameworks, mention a parameter for many times: Input voltage limits. This matters to a performance that carry puts: Course arrives course (Rail To Rail) , included input course to arrive to course and output course course. In applying actually, the engineer cares input voltage limits very much this parameter. Because stress the application of low power comsumption more very much currently, need low voltage power supply. For instance: To 3.3V power supply system, if carry puts an input cannot course arrives course, the voltage trends limits of the input can be compressed very low.

Course is put to rail transport

Alleged course is right course (amplifier of operation of Rail To Rail) , those who point to is amplifier input and be equal to value of power source voltage almost.

But above 3 kinds of frameworks that elaborate achieve course to arrive without real ground course, later development can share two kinds of brand-new frameworks, elaborate how to achieve course to arrive course.

Bipolar course inputs a framework to course

Interior of graph 4 ADA4099 inputs a framework

Interior of graph 4 ADA4099 inputs a framework

CMOS course inputs a framework to course

Interior of graph 5 ADA4505 inputs a framework

We discover not hard, with preamble 3 kinds do not support course to be compared to the input framework photograph of course, course is put when input to course input carry much more additional a pair of pipe, no matter be dynatron or MOS canal.

To Bipolar model for, after NPN inputs right input voltage limits, almost OK and patulous to course of positive electricity cause. After PNP inputs right input voltage limits, almost OK and patulous to course of negaive electricity cause. Actually, on two opposite power source way, bipolar carry is put accomplish course very hard to arrive absolutely course, because need assures certain abundant,the quantity makes dynatron is in to enlarge area.

To FET model for, and above Bipolar similar; But of FET pipe guide pressure fall very low, can make input voltage limits to be close to power supply voltage almost.

Carry puts hand in more lack fidelity

From above paragraphs elaborate can be informed: Arrive to achieve orbit course, when chip design engineer is designing chip, can use the pipe with two pairs of contrary polarity. In real work two pairs of pipe work alternately, when switch of two pairs of pipe, can appear lack fidelity phenomenon, we make the input that this phenomenon calls carry to put more lack fidelity. We pursue through falling (graph 6) thorough ground understands this phenomenon:

Graph 6 ADA4807 Vos and input in all modular voltage concerns

Graph 6 ADA4807 Vos and input in all modular voltage concerns

ADA4807 is course of a support arrives course is input-output amplifier of operation of nicety of high speed low a confusion of voices, below the circumstance of ± 5V power supply, it is probably when 4V, we can see Vos has rank jump. This it may not be a bad idea understands: When input report pressure ratio is inferior, use PNP pipe works, as the accretion that inputs voltage, NPN pipe begins to intervene, two kinds of pipe because of the character of itself and workmanship different brought about this result.

Graph 7 make more lack fidelity appearance

Pursue on (graph 7) showed carry is given off make more lack fidelity appearance now, in asking taller nicety measures a situation, should making more lack fidelity appearance is unallowed, how should that solve this problem?

ADI handles the solution that makes more lack fidelity issue

Plan adjusts the static work place of dynatron

Graph 8 AD8027/AD8028 adjusts static work place

Graph 8 AD8027/AD8028 adjusts static work place

This kind of means is not from go up at all improved hand in more lack fidelity, pass however external input voltage intervenes, change the static work place of dynatron, will hand in more lack fidelity dot to perhaps lose course to undertake moving moving to input voltage the right path, apply to input voltage not to try the case of full course.

Plan 2 inside buy charge pump charges beforehand technology

Graph pump of charge of the buy inside 9 AD8505 is eliminated hand in more lack fidelity

In-house charge pump uses a tall tension, can make input signal to pass a difference to cent is opposite and do not jump to another from beginning to end. On some kind of meaning, be divide from basic need hand in more lack fidelity.

Graph the Vos before technology of 10 charge pump is improved and Vcm concern

Graph the Vos before technology of 10 charge pump is improved and Vcm concern

Graph the Vos after technology of 11 charge pump is improved and Vcm concern

Plan framework of 30 drift Zero-drift

Framework of graph 12 ADA4528-1 Chopping+ACFB

Framework of graph 12 ADA4528-1 Chopping+ACFB

0 drift framework, will solve from another angle make more lack fidelity issue: Be patient of is handed in more lack fidelity, but can pass circuit corrective.

Graph 13 ADA4528-1 Vos and Vcm concern

Summary

When the engineer is undertaking chip is designed, to realize low power comsumption, used low voltage power supply; To realize bigger input voltage range, appeared course is designed to course. Make more lack fidelity issue to discovery again and think method to solve a problem, technical couple is real, ADI operation amplifier discovers to develop step by step in problem and the process that solve a problem in this kind just about.

Through above elaborate, believe what everybody understood carry is put not only to hand in more lack fidelity, the technology that puts to carry is made and how did in-house parts of an apparatus choose to also have more thorough knowledge better in process of chip design, design.

Reference material

ADI | Mixture signal and digital signal handle IC | Yadenuo semiconductor (Analog.com)

Saierjiou Folangge ” the circuit that is based on operation amplifier and analogue integrated circuit is designed ” press of Xi’an traffic university

Bichade Lazawei ” imitate CMOS integrated circuit is designed ” press of Xi’an traffic university

Avoid duty statement: The article is reprint an article, reprint this article purpose to depend on passing more information, the person that copyright puts in original work ‘s charge is all. If involve work copyright issue,article place uses video, picture, written language, contact please small make up undertake handling.

Recommend read:

Embedded microprocessor choice of the system

Close infra-red into picture: Newest 3D passes feeling technology to be able to reduce cost to simplify hardware framework

MPPT commonly used develop attacks principle and Ying Feiling implement a method

Uncover secret to heat up a design: The crucial password that integrated circuit designs

Semiconductor of international of the 6th Shenzhen exhibits SEMI-e, hua Weihua day grows the head enterprise such as electric Shanghai Hua Li to will be assembled in in June